Albert-Jan Yzelman

October 11, 2016

Parallel Computing & Big Data Huawei Technologies France

#### **BSP**

#### BSP machine = { sequential processor } + interconnect

The machine is described entirely by (p, g, L):

- strobing synchronisation,

- homogeneous processing,

- uniform full-duplex network,

#### **BSP**

BSP algorithm:

- strobing barriers

- full overlap

- *h*-relation bottlenecks: max<sub>s</sub>{sent<sub>s</sub>, recv<sub>s</sub>}

- work balance

L. G. Valiant, A bridging model for parallel computation, CACM, 1990

#### **BSP**

#### BSP cost:

$$T_{p} = \max_{s} w_{s}^{(0)} + L + \max\{\max_{s} w_{s}^{(1)} + L, \max_{s} h_{s}^{(1)}g + L\} + \dots$$

Separation of computation vs. communication.

L. G. Valiant, A bridging model for parallel computation, CACM, 1990

#### **BSP**

BSP cost:

$$T_{p} = \max_{s} w_{s}^{(0)} + L + \max\{\max_{s} w_{s}^{(1)} + L, \max_{s} h_{s}^{(1)}g + L\} + \dots$$

Separation of algorithm vs. hardware.

#### Immortal algorithms

The BSP paradigm, allows the design of immortal algorithms:

- given a problem to compute

- given a BSP computer (p, g, l)

- find the BSP algorithm that attains provably minimal cost.

E.g., fast Fourier transforms, matrix-matrix multiplication.

*Thinking in Sync*: the Bulk-Synchronous Parallel approach to large-scale computing. Bisseling and Yzelman, ACM Hot Topic '16.

http://www.computingreviews.com/hottopic/hottopic\_essay.cfm?htname=BSP

- 1: for  $j \mid \exists a_{ij} \neq 0 \in A_s$  and  $\pi_x(j) \neq s$  do

- 2: **get**  $x_{\pi_x(j),j}$

- 3: **sync** {execute *fan-out*}

- 1: for  $j \mid \exists a_{ij} \neq 0 \in A_s$  and  $\pi_x(j) \neq s$  do

- 2: **get**  $x_{\pi_x(j),j}$

- 3: **sync** {execute *fan-out*}

- 4:  $y_s = A_s x_s$  {local multiplication stage}

- 1: for  $j \mid \exists a_{ij} \neq 0 \in A_s$  and  $\pi_x(j) \neq s$  do

- 2: **get**  $x_{\pi_x(j),j}$

- 3: **sync** {execute *fan-out*}

- 4:  $y_s = A_s x_s$  {local multiplication stage}

- 5: for  $i \mid \exists a_{ij} \in A_s$  and  $\pi_y(i) \neq s$  do

- 6: send  $(i, y_{s,i})$  to  $\pi_y(i)$

- 7: **sync** {execute *fan-in*}

Variables  $A_s, x_s, y_s$  are local versions of the global variables A, x, y distributed according to  $\pi_A, \pi_x, \pi_y$ .

- 1: for  $j \mid \exists a_{ij} \neq 0 \in A_s$  and  $\pi_{\mathsf{x}}(j) \neq s$  do

- 2: **get**  $x_{\pi_x(j),j}$

- 3: **sync** {execute *fan-out*}

- 4:  $y_s = A_s x_s$  {local multiplication stage}

- 5: for  $i \mid \exists a_{ij} \in A_s$  and  $\pi_y(i) \neq s$  do

- 6: send  $(i, y_{s,i})$  to  $\pi_y(i)$

- 7: **sync** {execute *fan-in*}

- 8: for all  $(i, \alpha)$  received do

- 9: add  $\alpha$  to  $y_{s,i}$

Rob H. Bisseling, "Parallel Scientific Computation", Oxford Press, 2004.

Suppose  $\pi_A$  assigns every nonzero  $a_{ij} \in A$  to processor  $\pi_A(i,j)$ . If

- **2**  $\pi_{x}(j) \in \{s \mid \exists a_{ij} \in A, \pi_{A}(i,j) = s\};$

Suppose  $\pi_A$  assigns every nonzero  $a_{ij} \in A$  to processor  $\pi_A(i,j)$ . If •  $\pi_y(i) \in \{s \mid \exists a_{ij} \in A, \ \pi_A(i,j) = s\}$  and •  $\pi_x(j) \in \{s \mid \exists a_{ii} \in A, \ \pi_A(i,j) = s\};$

then

- fan-out communication scatters  $\sum_{j} \left( \lambda_{j}^{\mathsf{col}} 1

ight)$  elements from x,

- fan-in communication gathers  $\sum_i (\lambda_i^{\text{row}} 1)$  elements from y,

where

$$\begin{array}{lll} \lambda_i^{\mathsf{row}} &=& |\{s \mid \exists a_{ij} \in A_s\}| ext{ and } \ \lambda_j^{\mathsf{col}} &=& |\{s \mid \exists a_{ij} \in A_s\}|. \end{array}$$

Minimising the  $\lambda - 1$  metric minimises total communication volume.

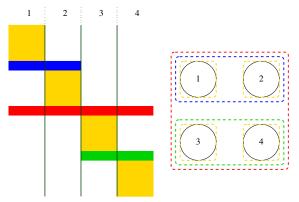

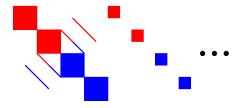

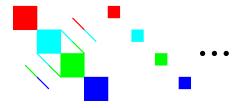

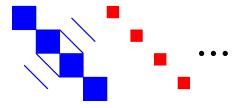

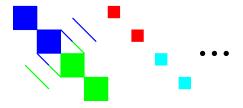

Partitioning combined with reordering illustrates clear separators:

- Group nonzeroes  $a_{ij}$  for which  $\pi_A(i) = \pi_A(j)$ ,

- permute rows *i* with  $\lambda_i > 1$  in between,

- apply recursive bipartitioning.

#### When partitioning in both dimensions:

Block:

$$\frac{2nz(A)}{p}(1+\epsilon) + n/p(\sqrt{p}-1)(2g+1) + 2l.$$

Block:

$$\frac{2nz(A)}{p}(1+\epsilon) + n/p(\sqrt{p}-1)(2g+1) + 2l.$$

Row 1D:

$$\frac{2nz(A)}{p}(1+\epsilon) + gh_{\text{fan-out}} + l.$$

Block:

$$\frac{2nz(A)}{p}(1+\epsilon) + n/p(\sqrt{p}-1)(2g+1) + 2I.$$

Row 1D:

$$\frac{2nz(A)}{p}(1+\epsilon) + gh_{\text{fan-out}} + I.$$

Col 1D:

$$\frac{2nz(A)}{p}(1+\epsilon) + \max_{s} recv_{s}^{\text{fan-in}} + gh_{\text{fan-in}} + I.$$

$$\begin{array}{ll} \text{Block:} & \frac{2nz(A)}{p}(1+\epsilon) + n/p(\sqrt{p}-1)(2g+1) + 2l. \\ \text{Row 1D:} & \frac{2nz(A)}{p}(1+\epsilon) + gh_{\text{fan-out}} + l. \\ \text{Col 1D:} & \frac{2nz(A)}{p}(1+\epsilon) + \max_s recv_s^{\text{fan-in}} + gh_{\text{fan-in}} + l. \\ \text{Full 2D:} & \frac{2nz(A)}{p}(1+\epsilon) + \max_s recv_s^{\text{fan-in}} + g(h_{\text{fan-out}} + h_{\text{fan-in}}) + 2l. \end{array}$$

Classical worst-case bounds (in flops):

$$\begin{array}{ll} \text{Block:} & \frac{2nz(A)}{p}(1+\epsilon) + n/p(\sqrt{p}-1)(2g+1) + 2l. \\ \text{Row 1D:} & \frac{2nz(A)}{p}(1+\epsilon) + gh_{\text{fan-out}} + l. \\ \text{Col 1D:} & \frac{2nz(A)}{p}(1+\epsilon) + \max_s recv_s^{\text{fan-in}} + gh_{\text{fan-in}} + l. \\ \text{Full 2D:} & \frac{2nz(A)}{p}(1+\epsilon) + \max_s recv_s^{\text{fan-in}} + g(h_{\text{fan-out}} + h_{\text{fan-in}}) + 2l. \end{array}$$

Memory overhead (buffers):

$$\Theta\left(\sum_{i}\left(\lambda_{i}^{\mathsf{row}}-1\right)+\sum_{j}\left(\lambda_{i}^{\mathsf{col}}-1\right)\right)=\mathcal{O}\left(p\sum_{\lambda:\lambda^{\mathsf{row}}\cup\lambda^{\mathsf{col}}}\mathbf{1}_{\lambda>1}\right).$$

Classical worst-case bounds (in flops):

$$\begin{array}{ll} \text{Block:} & \frac{2nz(A)}{p}(1+\epsilon) + n/p(\sqrt{p}-1)(2g+1) + 2l.\\ \text{Row 1D:} & \frac{2nz(A)}{p}(1+\epsilon) + gh_{\text{fan-out}} + l.\\ \text{Col 1D:} & \frac{2nz(A)}{p}(1+\epsilon) + \max_s recv_s^{\text{fan-in}} + gh_{\text{fan-in}} + l.\\ \text{Full 2D:} & \frac{2nz(A)}{p}(1+\epsilon) + \max_s recv_s^{\text{fan-in}} + g(h_{\text{fan-out}} + h_{\text{fan-in}}) + 2l. \end{array}$$

Memory overhead (buffers):

(

HUAWE

$$\Theta\left(\sum_{i}\left(\lambda_{i}^{\mathsf{row}}-1

ight)+\sum_{j}\left(\lambda_{i}^{\mathsf{col}}-1

ight)

ight)=\mathcal{O}\left(p\sum_{\lambda:\lambda^{\mathsf{row}}\cup\lambda^{\mathsf{col}}}\mathbf{1}_{\lambda>1}

ight).$$

Depending on the higher-level algorithm:

- fan-in latency can be hidden behind other kernels,

- fan-out latency can be hidden as well.

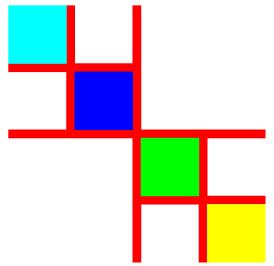

## Multi-BSP computer = p ( subcomputers or processors ) + *M* bytes of local memory+ an interconnect

Multi-BSP computer = p ( subcomputers or processors ) + *M* bytes of local memory+ an interconnect

A total of 4*L* parameters:  $(p_0, g_0, l_0, M_0, \dots, p_{L-1}, g_{L-1}, I_{L-1}, M_{L-1})$ . Advantages:

- memory-aware,

- non-uniform!

Multi-BSP computer = p( subcomputers **or** processors ) + M bytes of local memory+ an interconnect

A total of 4*L* parameters:  $(p_0, g_0, l_0, M_0, \dots, p_{L-1}, g_{L-1}, l_{L-1}, M_{L-1})$ . Advantages:

- memory-aware,

- non-uniform!

Disadvantages:

• (likely) harder to prove optimality.

L. G. Valiant, A bridging model for multi-core computing, CACM 2011.

#### An example with L = 3 quadlets (p, g, I, M):

$C = (2, g_0, I_0, M_0) (4, g_1, I_1, M_1) (8, g_2, I_2, M_2)$

Each quadlet runs its own BSP SPMD program.

SPMD-style Multi-BSP SpMV multiplication:

- define process 0 at level -1 as the Multi-BSP root.

- let process s at level k have parent t at level k 1.

- define  $(A_{-1,0}, x_{-1,0}, y_{-1,0}) = (A, x, y)$ , the original input.

SPMD-style Multi-BSP SpMV multiplication:

- define process 0 at level -1 as the Multi-BSP root.

- let process s at level k have parent t at level k 1.

- define  $(A_{-1,0}, x_{-1,0}, y_{-1,0}) = (A, x, y)$ , the original input.

- variables  $A_{k,s}, x_{k,s}, y_{k,s}$  are local versions of  $A_{k-1,t}, x_{k-1,t}, y_{k-1,t}$ ,

- $\{A, x, k\}_{k-1,t}$  was distributed into  $\tilde{p}_{k-1}$  parts,

SPMD-style Multi-BSP SpMV multiplication:

- define process 0 at level -1 as the Multi-BSP root.

- let process s at level k have parent t at level k 1.

- define  $(A_{-1,0}, x_{-1,0}, y_{-1,0}) = (A, x, y)$ , the original input.

- variables  $A_{k,s}, x_{k,s}, y_{k,s}$  are local versions of  $A_{k-1,t}, x_{k-1,t}, y_{k-1,t}$ ,

- $\{A, x, k\}_{k-1,t}$  was distributed into  $\tilde{p}_{k-1}$  parts,

- where  $\tilde{p}_{k-1} \ge p_{k-1}$  is such that all  $\{A, x, y\}_{k,s}$  fit into  $M_k$  bytes.

SPMD-style Multi-BSP SpMV multiplication:

- $\bullet$  define process 0 at level -1 as the Multi-BSP root.

- let process s at level k have parent t at level k 1.

- define  $(A_{-1,0}, x_{-1,0}, y_{-1,0}) = (A, x, y)$ , the original input.

- variables  $A_{k,s}, x_{k,s}, y_{k,s}$  are local versions of  $A_{k-1,t}, x_{k-1,t}, y_{k-1,t}$ ,

- $\{A, x, k\}_{k-1,t}$  was distributed into  $\tilde{p}_{k-1}$  parts,

- where  $\tilde{p}_{k-1} \ge p_{k-1}$  is such that all  $\{A, x, y\}_{k,s}$  fit into  $M_k$  bytes.

- 1: **do**

- 2: **for** j = 0 **to**  $\tilde{p}$  **step** p

- 3: **get**  $\{A\}_{k,j}$  from parent

- 4: down

- 5: while(up)

Mandatory input data movement only.

#### SPMD-style Multi-BSP SpMV multiplication:

```

1: do

2:

. . .

3:

for i = 0 to \tilde{p} step p

get \{A, x, y\}_{k,i} from parent

4·

5:

. . .

if(not down)

6:

compute y_{k,i} = A_{k,i} x_{k,i} {only executed on leafs}

7:

8:

. . .

9:

put y_{k,i} into parent

10:

. . .

11: while(up)

```

Mandatory and mixed mandatory/overhead data movement. Minimal required work only.

SPMD-style Multi-BSP SpMV multiplication:

#### 1: **do**

- 2:  $\forall j$ , **get** separator  $\tilde{x}_{k,j}$  and initialise  $\tilde{y}_{k,j}$  iff  $j \mod p = s$

- 3: for j = 0 to  $\tilde{p}$  step p

- 4: **get**  $\{A, x, y\}_{k,j}$  from parent

- 5: **sync**

- 6: **if**(not **down**)

- 7: compute  $y_{k,j} = A_{k,j} x_{k,j}$  {only executed on leafs}

- 8: perform fan-in on separator  $\tilde{y}_{k,j}$

- 9: **put**  $y_{k,j}$  into parent

- 10: **sync**

- 11: **put**  $\tilde{y}_{k,j}$  into parent and **sync**

- 12: while(up)

Mandatory costs plus overhead. Split vectors:  $\{x, y\}_s$  versus  $\{\tilde{x}, \tilde{y}\}_s$ .

Can we reuse existing partitioning techniques?

1 Partition  $A = A_0 \cup \ldots A_{p-1}$  with  $p = \pi_{l=0}^{L-1} p_l$ ?

No:  $A_s, x_s, y_s$  may not fit in  $M_{L-1}$ .

Can we reuse existing partitioning techniques?

- 1 Partition  $A = A_0 \cup \ldots A_{p-1}$  with  $p = \pi_{l=0}^{L-1} p_l$ ?

- 2 Find minimal k to partition A into s.t.  $\{A, x, y\}_i$  fits into  $M_{L-1}$ ?

- Very similar to previous work!

- Y. and Bisseling, "Cache-oblivous sparse matrix-vector multiplication by using sparse matrix partitioning", SISC, 2009.

- Y. and Bisseling, "Two-dimensional cache-oblivious sparse matrix-vector multiplication", Parallel Computing, 2011.

Can we reuse existing partitioning techniques?

- 1 Partition  $A = A_0 \cup \ldots A_{p-1}$  with  $p = \pi_{l=0}^{L-1} p_l$ ?

- 2 Find minimal k to partition A into s.t.  $\{A, x, y\}_i$  fits into  $M_{L-1}$ ?

- Very similar to previous work!

- Y. and Bisseling, "Cache-oblivous sparse matrix-vector multiplication by using sparse matrix partitioning", SISC, 2009.

- Y. and Bisseling, "Two-dimensional cache-oblivious sparse matrix-vector multiplication", Parallel Computing, 2011.

- 3 Hierarchical partitioning?

- $A = A_0 \cup \ldots \cup A_{k_0}$ ,

- $A_i = A_{i,0} \cup \ldots \cup A_{i,k_1}$ , etc.

- solves assignment issue.

Can we reuse existing partitioning techniques?

- 1 Partition  $A = A_0 \cup \ldots A_{p-1}$  with  $p = \pi_{l=0}^{L-1} p_l$ ?

- 2 Find minimal k to partition A into s.t.  $\{A, x, y\}_i$  fits into  $M_{L-1}$ ?

- Very similar to previous work!

- Y. and Bisseling, "Cache-oblivous sparse matrix-vector multiplication by using sparse matrix partitioning", SISC, 2009.

- Y. and Bisseling, "Two-dimensional cache-oblivious sparse matrix-vector multiplication", Parallel Computing, 2011.

- 3 Hierarchical partitioning?

- $A = A_0 \cup \ldots \cup A_{k_0}$ ,

- $A_i = A_{i,0} \cup \ldots \cup A_{i,k_1}$ , etc.

- solves assignment issue.

However,

all of these do *not* take into account different  $g_l!$

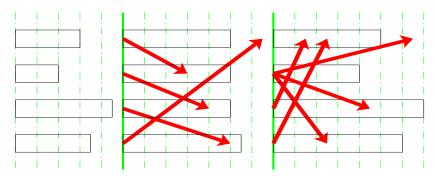

# Hierarchical partitioning

# Upper levelLower levelFan-out $6g_0$ Fan-in $2g_0$ Total: $8g_0 + \dots$

## Hierarchical partitioning

|         | Upper level     | Lower level |

|---------|-----------------|-------------|

| Fan-out | 6 <i>g</i> 0    | 0           |

| Fan-in  | $2g_0$          | 0           |

| Total:  | 8g <sub>0</sub> |             |

## Hierarchical partitioning

Upper level Lower level Fan-out 0 Fan-in  $4g_0$ Total:  $4g_0 + \dots$ Previous:  $8g_0$

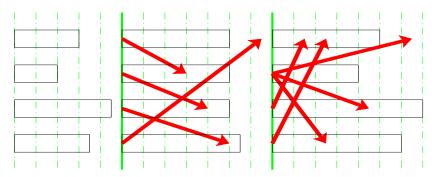

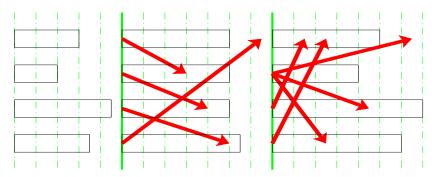

## Hierarchical partitioning

|                     | Upper level                                     | Lower level                        |

|---------------------|-------------------------------------------------|------------------------------------|

| Fan-out<br>Fan-in   | 0<br>4 <i>g</i> 0                               | 6g <sub>1</sub><br>2g <sub>1</sub> |

| Total:<br>Previous: | $\begin{array}{c} 4g_0+8g_1\\ 8g_0 \end{array}$ |                                    |

## Hierarchical partitioning

If  $g_0 < 2g_1$ , greedy hierarchical partitioning is suboptimal.

|                     | Upper level           | Lower level                        |

|---------------------|-----------------------|------------------------------------|

| Fan-out<br>Fan-in   | 0<br>4 <i>g</i> 0     | 6g <sub>1</sub><br>2g <sub>1</sub> |

| Total:<br>Previous: | $4g_0 + 8g_1 \\ 8g_0$ |                                    |

## Multi-BSP aware partitioning

Slightly modified V-cycle:

- coarsen

- recurse or randomly partition

- do k steps of HKLFM

- calculate gains taking  $g_0, \ldots, g_{L-1}$  into account

- In the second second

## Multi-BSP aware partitioning

Slightly modified V-cycle:

- coarsen

- recurse or randomly partition

- I do k steps of HKLFM

- calculate gains taking  $g_0, \ldots, g_{L-1}$  into account

- refine

**Claim**: if  $g_0 > g_1 > g_2 \dots$ , then HKLFM is a local operation.

By enumeration of all possibilities (L = 2). At level-1 refinement:

• suppose we move a nonzero  $a_{ij}$  from  $A_{s_1,s_2}$  to  $A_{t_1,t_2}$  with  $s_1 \neq t_1$ :

•

$$a_{ij} \in \tilde{A}_{s_1,s_2}, \ a_{ij} \notin \tilde{A}_{s_1}$$

: gain is  $g_1 - g_0$  or  $2(g_1 - g_0)$ .

•

$$a_{ij} \notin \tilde{A}_{s_1,s_2}$$

: gain is 0,  $g_1 - g_0$ , or  $2(g_1 - g_0)$ .

Hence it suffices to perform HKLFM steps on each level separately.

#### Summary

#### Differences from flat BSP:

#### • different notion of load balance

• parts must fit into local memory.

#### • non-uniform communication costs

• implies different partitioning techniques.

## Non-uniform data locality...

#### Summary

#### Differences from flat BSP:

#### • different notion of load balance

• parts must fit into local memory.

#### • non-uniform communication costs

• implies different partitioning techniques.

## Non-uniform data locality...

## with **fine-grained** distribution.

### How does it compare?

- ANSI C++11, parallelisation using std::thread,

- implementation relies on shared-memory cache coherency

- Mondriaan 4.0, medium-grain, symmetric doubly BBD reordering

- Global arrays without blocking, nonzero reordering, compression.

|      | matrix     | original | p = 1 | $p = \max$ | Optimal |

|------|------------|----------|-------|------------|---------|

| 2x8  | G3_circuit | 33.3     | 26.7  | 10.5       | 2.77    |

| 2x8  | FS1        | 83.5     | 65.3  | 22.0       | 10.3    |

| 2x8  | cage15     | 523      | 387   | 77.1       | 29.8    |

| 2×10 | G3_circuit | 22.7     | 16.9  | 9.77       | 1.73    |

| 2×10 | FS1        | 83.5     | 65.3  | 22.0       | 7.56    |

| 2x10 | cage15     | 341      | 233   | 54.7       | 23.4    |

all numbers are in ms.

- Y. and Bisseling, Cache-oblivious sparse matrix-vector multiplication, SISC 2009

- Y. and Roose, High-level strategies for sparse matrix-vector multiplication, IEEE TPDS 2014

### **Conclusions and Outlook**

Conclusions:

- not (yet) competitive on shared-memory

- programmability, usability?

- do we need to program for explicit hierarchies? (No!)

- is recursive SPMD general enough?

- Generic API, portability

- interoperability: call from MPI, BSP, Spark, ...

Future work:

- incorporate vector distribution

- distributed-memory, and shared memory without cache coherency:

- requires explicit Multi-BSP programming

- extension to sparse matrix powers

## Thank you!

## Backup Slides

HUAWEI

### Interoperable BSP

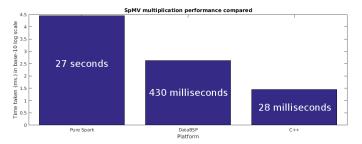

We have a shared-memory prototype. Preliminary results:

- SpMM multiply, SpMV multiply, and basic vector operations;

- one machine learning application.

Cage15, n = 5 154 859, nz = 99 199 551. Using the 1D method:

Note: this is ongoing work. Performance will be improved, and functionality will be extended.

## Interoperable BSP

Using an unified BSP guarantees interoperability. Going further:

- Call BSP algorithms from MPI;

- call BSP algorithms from MapReduce/Hadoop;

- call BSP algorithms from Spark;

• ...

Data I/O is a challenge. One example approach:

```

scala> val output_rdd = rdd.map( BSP_algorithm );

Hello from BSP, process number 0

Hello from BSP, process number 1

...

Hello from BSP, process number 11

scala>

```

Is this the best way to bridge HPC and Big Data?

### Multi-BSP broadcast example

```

do {

if (val != NULL )

bsp_put( val into process 0 );

bsp_sync()

} while( bsp_up() );

do {

if ( my process ID is not 0 )

bsp_get( val from process 0 );

bsp_sync();

} while( bsp_down() );

```

Automatically deploys over arbitrary hierarchies.

### Results: cross platform

Cross platform results over 24 matrices:

|                   | Structured | Unstructured | Average |

|-------------------|------------|--------------|---------|

| Intel Xeon Phi    | 21.6       | 8.7          | 15.2    |

| 2x Ivy Bridge CPU | 23.5       | 14.6         | 19.0    |

| NVIDIA K20X GPU   | 16.7       | 13.3         | 15.0    |

# no one solution fits all.

If we must, some generalising statements:

- Large structured matrices: GPUs.

- Large unstructured matrices: CPUs or GPUs.

- Smaller matrices: Xeon Phi or CPUs.

Ref.: Yzelman, A. N. (2015). Generalised vectorisation for sparse matrix: vector multiplication. In Proceedings of the 5th Workshop on Irregular Applications: Architectures and Algorithms. ACM.